● CPU 코어 아키텍처는 Cortex-A15을 확장

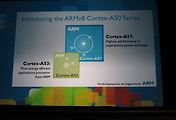

ARM은 64-bit의 새로운 CPU 코어 제품군 "Cortex-A50"를 발표했다. 고성능의 대형 CPU 코어 "Cortex-A57 (Atlas)", 저전력의 소형 CPU 코어 "Cortex-A53 (Apollo)"이다. 10 월 30 일부터 11 월 1 일까지 미국 산타 클라라에서 개최 된 ARM 기술 컨퍼런스 "ARM Techcon 2012"에서는 Cortex-A57/53 개요도 밝혀졌다.

ARM은 지금까지 약 2 년마다 CPU 코어 마이크로 아키텍처를 완전히 일신 해왔다. Cortex-A8, Cortex-A9, Cortex-A15는 처음부터 개발 한 새로운 코어를 투입 해왔다. 하지만 이번 64-bit 명령을 포함한 새로운 명령어 세트 아키텍처 "ARMv8"의 구현은 마이크로 아키텍처는 이전 세대의 확장으로 돌아 섰다. 64-bit 화라는 귀찮은 구현을 위해, 마이크로 아키텍처 자체는 어느 정도 확장하는 방법을 선택한 것 같다.

Cortex-A57는 고성능 모바일 기기나 서버, 네트워크 인프라 등을 포함한다. ARM은 최고급 CPU에서 싱글 스레드 성능을 개선하고 있는데, Cortex-A57도 Cortex-A15보다 단일 스레드 성능을 올린다. Cortex-A9 이후 ARM의 CPU는 최대 4코어에서 1클러스터를 형성하고, L2 캐쉬와 시스템 버스 인터페이스를 공유한다. Cortex-A57도 마찬가지로 4코어 1클러스터를 짠다.

기존의 ARM 코어 L1 캐시 크기가 가변 마이크로 아키텍처가 많았지 만, Cortex-A57는 L1 캐시 크기는 고정되어있다. L1 명령 캐쉬는 48KB, L1 데이터 캐시는 32KB에서 명령어 캐시가 Cortex-A15보다 증량되고있다. L2 캐시의 크기가 다양하고, 512KB, 1MB, 2MB의 구성이이 준비되어있다. 서버도 대상으로하기 때문에 캐시 ECC 등이 옵션으로 준비되어있다.

Cortex-A57는 시스템 버스도 확장되었다. 종래는 "CCI (Cache Coherent InterConnect) -400 '로 불리는 버스에서 클러스터를 연결하고 있었지만, 서버 전용의 대형 구성에서는"CCN (Cache Coherent Network) -504'로 불리는 버스로 16 코어까지 연결한다. CCN-504는 클러스터간에 공유 L3 캐시도 지원한다.

|  |  |

|  |

● 아웃 오브 오더 실행의 자원을 강화

Cortex-A57는 Cortex-A15 아키텍처를 기반으로 확장하고있다. 아래는 Cortex-A15의 파이프 라인이지만, Cortex-A57의 파이프 라인 구조는 비슷하다. 양자의 가장 큰 차이는 말하는 동안도 아니고 64-bit 명령 지원하지만, Cortex-A57는 32-bit시와 64-bit시 모두에서 높은 성능을 달성 할 수 있도록 최적화되어있다.

ARM Cortex-A15 블록 다이어그램

또한, Cortex-A57는 "현대적인 워크로드"에 최적화되어 있다고한다. 하이엔드 모바일 제품이나 네트워크 서버의 워크로드에서 캐시 나 Translation Lookaside Buffer (TLB) 지점 버퍼에 압력의 증가를 예상하고있다. 또한 온칩 메모리 계층에 성능 의존의 증대도 상정하고, 그러한 작업에 대한 확장이 이루어지고있다.

Cortex-A15은 전체의 아웃 오브 오더 실행의 슈퍼 스칼라 파이프 라인이지만, Cortex-A57도 마찬가지로, Cortex-A15보다 아웃 오브 오더 실행을위한 자원이 강화되고있다. 이에 따라 1클럭 당 병렬로 실행할 수있는 명령 수를 늘리고, 명령 레벨의 병렬성을 강화하고있다.

L1 명령 캐쉬는 48KB의 3-way 세트 연관 티브에서 L1 TLB도 48 항목과 강화되고있다. L1은 명령 프리 페처와 함께하고있다. 분기 예측기구는 분기 대상 버퍼 (BTB)는 2K ~ 4K 항목과 Cortex-A15의 256 항목보다 크게 강화되었다.

명령 디코드는 Cortex-A15과 같은 3 계명 / 사이클. Cortex-A9에서 Cortex-A15는 디코딩 명령은 2 명령에서 3 명령에 확장되었지만, Cortex-A15에서 Cortex-A57는 증가하지 않았다. 그러나, 레지스터 리 네이밍이나 인플 명령 수의 윈도우는 Cortex-A15보다 강화되고, 따라서 실질적으로 많은 명령을 병렬 실행할 수있다. 예를 들어, 인 비행 제어 할 명령은 Cortex-A15는 2010 년의 "Linley Tech Processor Conference"에서 최초 발표시에는 60 명령과 설명했지만, Cortex-A57는 128 명령으로 늘고있다.

● 정수계에서 4 포트의 명령 실행 파이프 라인

Cortex-A57의 정수계 실행 파이프 명령 디스패치 포트는 총 4. 이것도 Cortex-A15와 마찬가지로 간단한 정수 연산 파이프 라인이 2 분기가 1, 곱하기와 나누기의 파이프 라인이 1 구성 보인다. 별도의 스케줄러 큐를 갖춘다. 포트 수는 같지만, 정수 연산은 64-bit 화에서 연산 유닛도 64-bit 화하고있다.

부동 소수점 연산 / SIMD 엔진은 Cortex-A57의 개선 사항 중 하나입니다. 부동 소수점 연산은 IEEE754-2008 규격이며, ARMv8에서 참가한 암호화 처리 명령의 가속 장치도 구현됐다. ARM 명령어의 SIMD 명령이다 NEON을 지원하는 FP / SIMD 유닛은 단 정밀도 32-bit 경우 4 병렬 운영 / 사이클 처리량이다.

로드 / 스토어 유닛도 Cortex-A15와 마찬가지로 2 포트 구성. Cortex-A57는 데이터의 종속성을 예측 한 아웃 오브 오더로드 / 스토어를 실행할 수있다. L1 데이터 캐시는 32KB에서 2-way. 32 항목의 TLB가 포함되어 있으며, 데이터를 예측하는 하드 프리 페처를 갖춘다. 64 bit CPU 인 Cortex-A57의 주소 공간은 48-bit 가상 메모리 공간 ,44-bit 실제 메모리 공간.

L2 캐시는 2MB까지 16way 세트 연관 티브. 코어 당 L2 대해 인터페이스와 L2에 대한 하드웨어 프리 페처도 갖춘다.

Cortex-A57의 성능은 ARM의 발표는 Cortex-A15에 32-bit시 25 % 이상 늘어난다. 1.7GHz 때의 CPU 성능은 기존의 벤치 마크 SPECINT2000에서 1250 점수와 ARM은 추정하고있다. 아래는 1.4GHz의 Cortex-A9을 1로했을 경우의 CPU 성능 비교 예상에서 쿼드 코어 구성의 것이다. 보라색의 라인이 Cortex-A9 1.4GHz, 빨간색 선이 Cortex-A15 1.5GHz, 녹색 선이 Cortex-A57 1.7GHz이다. 또한 비교 용으로, Intel의 Atom N570도 추가되고 있지만, 까다로운 데, 이것은 듀얼 코어로, Hyper-Threading에 따르면 4 스레드 것으로 보인다.

Cortex-A57의 평면도 예는 아래 그림과 같다. 그림의 녹색 부분이로드 / 스토어에서 보라색이 명령어 인출, 황색을 디코딩, 빨강과 파랑이 실행 유닛 군이다. Cortex-A57의 평면도도 Cortex-A15와 비슷하다. 100 % 합성이 가능하고, 이미 RTL은 라이센스 사용자에 걸쳐있다.

Cortex-A57는 단독으로 사용되는 외에 소형 코어 Cortex-A53와 함께 big.LITTLE 구성에서도 사용되는 것을 상정하고있다.

ARM은 Cortex-A57을 투입 한 후에도 Cortex-A15을 계속하면 ARM Techcon의 프레스 브리핑에서 설명했다. 서버 등의 새로운 시장은 신속하게 64-bit의 Cortex-A57로 이행하는 것으로 보이지만, 모바일에서는 32-bit 전통적인 ARMv7 명령어 CPU 코어가 남아있을 가능성이 높다. 따라서 Cortex-A57가 등장한 후에도 Cortex-A57와 Cortex-A15가 스마트 폰 및 태블릿 시장에서 병존 할 것으로 보인다.

'IT/Hardware > CPU/MB' 카테고리의 다른 글

| 인텔 하즈웰CPU 제품스펙 공개 (0) | 2012.12.13 |

|---|---|

| 2013 AMD 로드맵의 변화와 차세대 콘솔게임기의 출시행방 (0) | 2012.11.28 |

| 인텔 하즈웰ULT에서 보여준 CPU통합칩 가능성 (0) | 2012.11.25 |

| 인텔 60코어「Xeon Phi」를 정식 발표 (0) | 2012.11.16 |

| TSMC 20nm 16nm 기술 로드맵을 발표 (0) | 2012.11.16 |

| ARM 차기 아키텍쳐 Cortex-A57과 Cortex-A53을 발표 (0) | 2012.11.03 |

| 윈도우8 타블렛을 시작으로 본격 시동을 거는 인텔의 모바일전략 (5) | 2012.11.03 |

| 인텔, 아톰 Z2760 스펙공개 정식출시 (2) | 2012.10.25 |

| AMD 2세대 파일드라이버아키텍쳐 비세라CPU 출시 (0) | 2012.10.23 |

| 소니 플스3 슈퍼슬림 반도체 변화 (0) | 2012.10.21 |

댓글