반응형

플래쉬메모리와 그 응용에 관한 세계 최대의 행사가 미국 캘리포니아주 산타클라라에서 개최되었다.

Flash Memory Summit는, 강연회와 전시회로 구성되어 있다. 메인 이벤트는 강연회에서, 테마별의 강연 세션과 전체 강연인 키노트 세션 및 프리젠테이션 있다.

테마별의 세션은 5개 전후의 강연이 동시 진행하고 있어, 이것이 3일간 계속 된다. 꽤 대규모 강연회이다

테마별의 세션은 5개 전후의 강연이 동시 진행하고 있어, 이것이 3일간 계속 된다. 꽤 대규모 강연회이다

첫날의 키노트 세션에서는, NAND 플래쉬 메모리 및 DRAM의 대기업 메이커이며, 각종의 차세대 불휘발성 메모리의 개발에 임하고 있는 SK하이닉스가 반도체 메모리의 장래를 전망했다.

●DRAM와 NAND 플래시가 미세화의 한계에

강연자는 연구 개발 담당 부사장을 맡은 박성욱씨는, 강연 타이틀은 「Prospect for New Memory Technology」이다.

박성욱씨는 먼저 DRAM의 비트 비용 (저장용량 당 가격)이 지난 20년에 연평균 33 %의 비율로 감소 해 온 것을 말했다. 그리고 향후이 추세를 유지할 수 있을지 여부는 극히 불투명 해지고 있다고했다. 연평균 20 % 정도의 비트 비용 감소에 머무를 가능성도 적지 않다.

그 큰 이유는 DRAM 셀 커패시터의 미세화가 어려워지고있는 것에있다. DRAM 셀 커패시터는 정전 용량을 유지하기 위해, 길쭉한 원통형으로되어있다. 미세화는 원통형의 직경을 가늘게하고 높이를 올리는 것에 다름 아니다. 가로 세로 비율 (A / R : 화면 비율)로 보면, 3xnm 세대의 DRAM 셀 커패시터에서는 A / R이 25에 달하고있다. 세계에서 가장 높은 인공 구조물 인 'Burj Khalifa (버즈 하리화) "(아랍 에미리트 두바이)의 A / R이 6 인에서도, DRAM 셀 커패시터의 굉장함을 엿볼 수있다. 그리고 또한 A / R을 올리는 것은 매우 어려워지고있다. 이 것이 2xnm 세대 이후의 미세화를 막고있다.

NAND 플래시 메모리는 지난 8 년간 연평균 50 %의 비율로 실리콘 면적당 기억 비트 (기억 용량)를 증대시켜왔다. 거의 1 년 간격으로 미세 가공 치수 세대 교체하는 급격한 밀도를 달성 해왔다. 그러나 지금에 와서, NAND 플래시도 미세화에 갑자기 제동되고있다.

그 이유의 하나는 1개의 메모리 셀이 축적 전자의 수가 적어 온 것이다. 1xnm 세대 이후가되면, 10 개 정도의 전자를 제어해야한다. 이러한 섬세한 제어가 매우 어렵다.

또한 인접 셀 간의 간섭 제어 게이트의 보이드 (공극) 발생, 비트 선 부하의 증대, 워드 선간 누설 증가 등의 문제가 미세화에 의해 악화되고있다. 게다가 현재 명확한 해결책을 얻을 수 없다.

●NAND플래시의 3차원화

NAND 플래시 메모리의 미세화 한계를 돌파하는 기술의 후보로 3 차원 화 (3D NAND)이있다. NAND 플래시 메모리의 메모리 셀은 셀 문자열이라고 늘어서로 구성되어있다. 셀 문자열은 실리콘의 평면 방향으로 뻗어있다. 이를 직각으로 구부리고 실리콘 표면과 수직 인 방향으로 셀 문자열을 형성하는 것이 "3D NAND"이다.

"3D NAND"는 원리 적으로는 매우 높은 밀도를 노릴 수 있지만, 한편으로 제조 기술이 매우 복잡된다는 문제를 안고있다. 생산 수율을 확보 할 수 있는지가 우선 큰 문제가된다. 또한 데이터 보존 기간 저하라는 문제가있다. 성막 수준에서 결함이없는 메모리 셀을 실현해야한다.

3D낸드의 과제

3D낸드의 구조들..

●차세대 메모리로 미세화의 한계를 넘는다

DRAM와 NAND 플래시의 모두가 한계를 보이는 가운데, 기대가 걸리는 것이 「차세대 메모리(New Memory)」이다.DRAM 및 NAND 플래시보다 원리적으로는 미세화가 진행되는 것과 동시에, 신뢰성을 확보할 수 있다.

박성욱씨는, 기억용량(밀도)을 세로축에, 성능・신뢰성을 횡축에 두어 NAND 플래시를 용량 중시 타입, DRAM를 성능 중시 타입의 메모리라고 평가했다.그리고 차세대 메모리(New Memory)를, 양자를 잇는 존재로서 도시해 보였다.

차세대 메모리의 가능성에는, 3개의 방향이 있다.

차세대 메모리의 가능성은 3가지 방향이있다.

하나는 기존의 메모리 (DRAM 또는 NAND 플래시 메모리)의 대체이다.

다른 하나는 시스템의 성능 향상이다. 대기 시간을 줄이거 나 소비 전력을 낮추고한다.

마지막은 미세화를 더 진행할 것이다. 비트 비용을 낮추고, 폼 팩터를 줄일 방향이다.

차세대 메모리의 가능성은 3가지 방향이있다.

하나는 기존의 메모리 (DRAM 또는 NAND 플래시 메모리)의 대체이다.

다른 하나는 시스템의 성능 향상이다. 대기 시간을 줄이거 나 소비 전력을 낮추고한다.

마지막은 미세화를 더 진행할 것이다. 비트 비용을 낮추고, 폼 팩터를 줄일 방향이다.

그 차세대 메모리 기술은 주로 3개의 후보가있다. 상변화 메모리 (PCRAM), 스핀 주입 메모리 (STT-RAM), 저항 변화 메모리 (ReRAM)이다.

각각의 위치는 스핀 주입 메모리 (STT-RAM)가 고성능 · 고 신뢰성,

저항 변화 메모리 (ReRAM)가 고밀도

상변화 메모리 (PCRAM)가 양자의 중간이다.

각각의 위치는 스핀 주입 메모리 (STT-RAM)가 고성능 · 고 신뢰성,

저항 변화 메모리 (ReRAM)가 고밀도

상변화 메모리 (PCRAM)가 양자의 중간이다.

박성욱씨는 그리고, 각 후보의 장점과 단점을 해설했다.

상변화 메모리(PCRAM)의 장점은 우선, 재료가 잘 알려져 있는 것이다.카르코게나이드로 불리는 게르마늄, 안티몬, 테룰의 합금은 과거부터 상전이(결정상과 아몰퍼스(amorphous)상을 왕래하는 것)를 일으키는 것으로 알려져 있어 광디스크나 광카드 등에도 응용되었던 적이 있다.미세화의 한계가 먼 것도 특징이다. 5nm의 치수로 가공해도 메모리 소자로서의 성질을 잃지 않는다.

상변화 메모리(PCRAM)의 장점은 우선, 재료가 잘 알려져 있는 것이다.카르코게나이드로 불리는 게르마늄, 안티몬, 테룰의 합금은 과거부터 상전이(결정상과 아몰퍼스(amorphous)상을 왕래하는 것)를 일으키는 것으로 알려져 있어 광디스크나 광카드 등에도 응용되었던 적이 있다.미세화의 한계가 먼 것도 특징이다. 5nm의 치수로 가공해도 메모리 소자로서의 성질을 잃지 않는다.

상변화 메모리(PCRAM)는, DRAM 또는 NAND 플래시를 직접 옮겨놓는 것은 어렵다.그 대신에, 시스템의 성능을 향상시키는 새로운 메모리 계층을 만들어 낼 수 있을 가능성이 있다.

문제는 제조단가이다. 비트 코스트로 DRAM의 2분의 1 정도를 실현할 수 있을지. 소비 전력에도 문제가 있다. 리셋 전류가 비교적 크고, 어떠한 대책이 요구된다.

이어 스핀 주입 메모리 (STT-RAM) 장점은 HDD 자기 헤드에서 입증 된 "자기 터널 접합 (MTJ)"를 기억 소자로 사용하는 것이다. 고속으로 동작하며, 10nm 미만의 미세한 크기로도 움직인다. 따라서 워크 메모리로서 미래는 DRAM을 대체하는 것이 아니냐는 기대가 걸린다. 그러나 제조 비용의 제약이 어려워 고속 성능은 STT-RAM은 DRAM에 비해 우수하다고는 말할 수 없다. 아직 개발의 여지가있다.

그리고 저항 변화 메모리 (ReRAM)는 기억 소자의 재료와 구조가 단순하게, 낮은 소비 전력으로 동작하게 특징이있다. 구조가 간단하기 때문에 기억 소자 층을 적층함으로써 기억 밀도를 증가시키기 쉽다. 고밀도 대용량 방향이라고 할 수있다. 그러나 스위칭기구는 얼마든지 존재하고 스위칭 메커니즘은 반드시 명확하게하고 있지 않다. 이 점은 여전히 큰 과제가되고있다.

SK하이닉스가 생각하는 차세대 메모리에 의한 메모리 계층

그리고 박성욱씨는, SK하이닉스가 생각하는 장래의 메모리・아키텍쳐를 나타냈다. CPU를 맨 위에, 바로 아래에 STT-RAM가 온다. 기존의 메모리 계층은 SRAM과 DRAM에 상당하는 부분이다. 그 아래에 PCM이 놓인다. 워크 메모리 (DRAM) 및 스토리지 (NAND 플래시 메모리)의 성능 격차를 해소 메모리이다. 그리고 NAND 플래시 메모리 커버 부분에는 ReRAM이두고 변화하는 시나리오이다.

SK Hynix는 현재, 이러한 차세대 메모리 기술의 개발을 모두, 다루고 있다.독특한 것은 모두가 단독 연구가 아니고, 공동 개발인 것이다.게다가 메모리 기술 마다, 개발 파트너 기업이 다르다.STT-RAM는 도시바와 PCRAM는 IBM과 ReRAM는 HP와 공동 개발중이다.

다만, 콘트롤러기술만은, 콘트롤러 개발 기업의 Link A Media Device(LAMD)를 매수하는 것으로 자사 기술에 수중에 넣었다.SSD(Solid State Drive)를 비롯한 응용 제품을 개발할 경우에, 콘트롤러 기술은 빠뜨릴 수 없다.

반응형

'IT/Hardware > Storage' 카테고리의 다른 글

| HGST 헬륨를 충전한 하드디스크 공개 (0) | 2012.09.14 |

|---|---|

| 웬디 울트라북 초슬림 5mm 하드디스크 출시 (0) | 2012.09.13 |

| 르네사스 USB 3.0지원 4포트 허브 컨트롤러 발표 (0) | 2012.09.10 |

| SSD 수명의 문제점과 해결방안 (0) | 2012.09.09 |

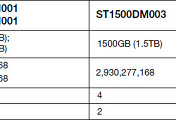

| 시게이트 ST2000DM001 1테라 플래터 유통중 (29) | 2012.09.06 |

| 웬디 1TB 플래장 1장 적용한 캐비어 블루(WD10EZEX-00RKKA0) 벤치 (0) | 2012.08.08 |

| 웨스턴 디지털, NAS최적화 하드디스크 "웬디 레드" 출시 (0) | 2012.07.11 |

| 플렉스터(Plextor) M5 SSD 출시 (0) | 2012.07.04 |

| 하이닉스, 26나노 MLC SSD 출시 (0) | 2012.06.25 |

| 삼성전자, 세계 최초 27나노 모바일메모리 양산 (0) | 2012.05.17 |

댓글