●Windows 8 타블렛시장의 침투를 노리는 Clover Trail

드디어 등장한 Microsoft의 반격의 히든 카드 "Windows 8" 그리고, Windows 8과 함께 부상하고있는 것은, x86 계 CPU 기반의 Windows 8 태블릿이다. ARM 버전의 Windows RT에 대한 불안에서 x86의 Windows 8 태블릿에 대한 기대가 높아지고있다. 그리고, Intel은이 타이밍에 맞춰 태블릿용 SoC (System on a Chip) "Clover Trail (클로버 트레일)"를 급히 투입했다. Intel은, Windows 8에서 Clover Trail에서 태블릿을 부각시켜, 장래는 스마트폰에도 Atom SoC를 침투시키고 싶은 곳이다. 사실, Microsoft는 ARM 기반의 Windows RT 버전의 Surface를 Windows 8 동시에 투입하는 등, Windows RT에도 힘을 넣고 있기 때문에, Intel의 예측대로 될지 어떨지는 모른다. 그러나, Intel은, Windows 8 태블릿을 시작으로 싸우고 싶은 것이다.

<클로버트레일과 메드필드의 차이점>

Intel이 운이 좋은 것은, Clover Trail이나 스마트 폰용 Medfield (메드필드)이 칩의 성능과 전력소모, 제조 비용 등의면에서 일정한 경쟁력이있는 것이다. 지금까지의 Intel의 모바일 플랫폼은 모두 전력 등에 문제가있어 ARM 기반의 모바일 SoC와 경쟁하기는 어려웠다. 원래 모바일 용 칩은 애플리케이션 프로세서 (CPU 코어)를 중심으로 각종 코어와 I/O를 모두 가져온 SoC되어있는 것이 보통인데, Intel의 Atom 기반의 모바일 제품은 SoC에조차되어 없었다. SoC 된 것은 이번 Medfield / Clover Trail 세대 에서다.

아톰CPU는 점점 통합칩으로 진화중이다.

그런 의미에서 Medfield / Clover Trail은 Intel에있어서, 드디어 모바일 시장의 요구 사항에 따라 잡았다 하겠다. 이전에는 제대로 싸울 모바일 제품에서는 없었던 것이 이제는 싸움을 시작할 수있다. 다이크기으로 봐도 현재 제품이라면 비용면에서 결코 Intel 쪽이 높은 것은 아니다.

Intel은 LPIA이라고했다 Atom 계획을 시작했을 때부터, 모바일 시장을 대상으로했다. 원래, Atom의 "Bonnell (본널)"코어 Snapdragon의 "Scorpion (스콜피온)"코어에 대항하여 성능이 설정되었다. 그런데도, 본격적인 모바일 SoC를 만들 때까지, 왜 이렇게 시간이 걸려 버린 것이다. 그것은, 모바일 애플리케이션 프로세서에 알지못하는 Intel은 안되는 장애가 많았기 때문이다.

● SoC를위한 공정 기술의 개발이 필요했다

Intel의 경우, 프로세서는 자사 Fab에서 제조, SoC 화는 프로세스 기술 사양의 확장이 필요했다. 원래, Intel의 첨단 프로세스 기술은 고속 로직에 최적화되어 있으며, SoC에 필요한 사양이 부족했다. 첨단 프로세스에 SoC에 필요한 사양를 주입하기 시작한 것은 45nm 공정부터, Intel 프로세서를위한 45nm 프로세스 "P1266"의 파생에서 SoC를위한 과정 "P1266.8"를 2008 년경에 시작한 .

IEDM의 발표 만 보면 P1266.8은 최대한 SoC 화를 가능하게하는 공정 기술처럼 보인다. 그러나 실제로는 45nm 프로세스의 모바일 플랫폼 Moorestown은 CPU에 노스 브릿지 칩 기능을 통합 한 "Lincroft (링크 로프트)"와 I/O 사우스브릿지"Langwell (랭웰)"의 2 칩 구성에서 원 칩의 SoC는되어 있지 않았다 (가전 제품은 SoC). I/O를 포함 Langwell는 TSMC의 65nm 공정으로 제조되어 있었다. 모처럼의 45nm SoC 프로세스의 특징을 많이 사용되지 않는다.

45nm에서 SoC 프로세스는 P1266.8라는 어중간한 번호로부터도 추측 할 수 있도록 다분히 시험적인 과정 인 것 같다. Intel이 주력 모바일 제품을 SoC 공정 기술로 SoC 화까지는 이르지 않았다. 45nm SoC 프로세스는 3.3V의 I/O 트랜지스터가 실제로 제공되지 않았다는 보도도 있었다.

● 32nm 프로세스로 SoC 프로세스를 강하게 밝힌 Intel

Atom 기반의 모바일 제품의 SoC 원칩화는 32nm 프로세스 세대까지 미루어졌다. 32nm에서 프로세서 전용이 "P1268", SoC 전용이 "P1269"가되어, 번호에서도 SoC 프로세스가 명확하게 구별되었다. 또한 45nm 때는 Intel은 SoC 프로세스의 설명을별로 미디어 용으로는하지 않았다는가 32nm에서 일전 해 SoC 프로세스를 크게 내세우고 설명하기 시작했다. 이 근처의 변화에서 Intel이 32nm의 SoC 프로세스에 자신감있는 것을 알 수있다. 아래는 2009 년 9 월의 Intel Developer Forum (IDF)에서, 32nm SoC 프로세스 설명 슬라이드 다.

|  |  |

|  |  |

그리고, Intel이 자신감이 32nm SoC 과정에서 만들어진 최초의 모바일 SoC가 Medfield의 Penwell와 이번 Clover Trail의 Cloverview이다. 즉, Intel은 SoC 제품을 만들기 위해 먼저 공정 기술의 개발에서 시작해야하며, 따라서만으로도 상당한 시간을 할애해야했다.

게다가 SoC 프로세스 화는 Intel의 공정 기술의 선도도 희생되었다. 먼저 첫 번째 45nm 공정 세대에서는 프로세서의 성능 프로세스와 SoC의 프로세스는 제품 출시시기에 큰 차이가있어 실제로는 SoC 프로세스는 지연이었다. 45nm 모바일 칩이 등장했을 무렵에는 PC용 CPU는 32nm 공정 버전이 등장하려고하고 있었다. PC용 프로세스보다 최종 제품의 투입이 1프로세스 세대 늦었다. 같은시기에 주요 파운드리는 40nm 공정의 제품을 출하하고, Intel의 최대 강점 인 공정 기술의 선도는 소멸 된 셈이다.

32nm SoC 프로세스는 45nm보다 개발 속도 한 것이지만, 32nm에서도 모바일 Atom 제품의 투입 역시 PC용 프로세스 주회 지연되고있다. PC용 CPU는 22nm에 이행이 시작하고 있는데, Atom 기반의 모바일 SoC는 올해 들어 32nm 프로세스 Penwell과 Cloverview가 너무 늦게 등장했다.

● 미묘하게 바뀌고있는 22nm 버전의 SoC 프로세스 계획

Intel은 향후 프로세서용 프로세스와 SoC 프로세스의 시간 차이를 줄일 방침이다 22nm 세대용은 Intel은 내년 (2013 년) 말까지 22nm SoC 프로세스의 Atom을 투입 할 예정이다. 조금 재미있는 것은이 22nm SoC 프로세스 계획이다. 22nm SoC의 특징을, Intel은 미묘하게 변화하고있다.

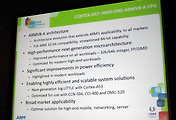

아래의 슬라이드 중 왼쪽은 Intel이 2011 년 IDF에서 설명한 22nm SoC 프로세스의 특징 목록. 오른쪽은 올해 (2012 년)의 IDF에서 나타난 22nm SoC 프로세스의 특징 목록이다.

|  |

2011 년에 보여 준 22nm SoC 프로세스의 특징리스트 2012 년에 보여 준 22nm SoC 프로세스의 특징리스트

이 2개의 슬라이드의 차이는 명료해 지난해 계획은 22nm 프로세스에서 3.3V의 I/O 트랜지스터를 지원하지 않는 것이었다 것이 올해의 계획은 더 해지고있다. 이미 설명했듯이, 평면 트랜지스터는 논리 트랜지스터는 구조적으로 크게 바꾸는 것으로, 고전압 용 I/O 트랜지스터를 실현했다. 트라이 게이트 된 22nm는 평면과는 다른 기술로이 문제를 해결해야한다. 지난해부터 올해 사이에 기술적으로 3.3V의 지원을 추가하는 것이라는 전망이 서 있었을지도 모르지만, 여기가 큰 차이가있다. 이 변경이 의미하는은 22nm SoC 과정에서도 Intel은 SoC에 필요한 I/O를 완벽하게 지원 할 수 있다는 것이다.

명확한 것은, Intel이 모바일 SoC를 런칭함에있어 공정 기술에서 혁신해야하고, 거기에 시간이 걸린 것이다. 그리고 지금은이 문제를 해결할 수 있으며, 다음은 SoC의 프로세스 기술을 업계 선두로 되찾으려하고있다.

● 2 단계의 시스템 버스를 갖춘 SoC의 내부 구조

SoC 화에 따라 Intel 칩의 내부 구조도 변경했다. Medfield를 보면 Penwell SoC 내부는 2층의 인터커넥트 패브릭으로 분리되어있다. 칩의 시스템 버스가 2 계층 구조로되어있다. "North SoC Interconnect"는 CPU 코어와 GPU 코어와 비디오 엔진, 디스플레이 컨트롤러와 메모리 컨트롤러를 연결한다. 기존의 노스 브릿지 칩 측의 상호 연결이다. "South SoC Interconnect"는 기타 I / O 장치 및 구성 요소를 연결하는 기존의 사우스 브릿지 부분의 측 인터커넥트이다.

메드필드의 상호연결구조

이 2 계층의 내부 인터커넥트 구조에, Intel은 금년 2월의 ISSCC(IEEE International Solid-State Circuits Conference)로 설명을 행하고 있다.아래가 RF트랜시버를 통합한 Atom SoC의 시작칩 「Rosepoint」의 블럭도다.Rosepoint에서는, CPU 코어를 접속하는 North SoC Interconnect는 「Memory Fabric(메모리패브릭)」, I/O를 접속하는 South SoC Interconnect측은 「IOSF(Intel On-die Switch Fabric)」가 되고 있다.Intel의 SoC의 설명도에서는, Memory Fabric 부분은 「Memory Interconnect」가 되고 있는 그림도 있다.사우스측도 이와 같이 「Intel's Interconnect Fabric」가 되고 있는 그림이 있다.Intel은, 작년무렵부터 IOSF를 자사의 표준 내부 버스로 하려고 하고 있으면 보도되고 있다.명칭은 달리해, 내용적으로는 같은 것이라고 생각된다.

Memory Fabric라는 명칭은 메모리 대역폭에 맞게 스케일시키는 것부터 붙여진 것으로 추측된다. SoC 세대 메모리 인터페이스가 바뀔 때마다 사양이 바뀔 것으로 보인다. 메모리 액세스가 중요한 CPU 코어와 그래픽 주위의 구성 요소는 모두 여기에 Memory Fabric / North SoC Interconnect에 연결되어있다.

● CPU 코어와 GPU 코어의 성능을 이끌어내는 버스

종래의 Intel의 45 nm판 듀얼 코어 Atom 제품에서는, 시스템 버스와 Atom 코어간의 인터커넥트가 성능 병목이되어 있었다고 한다.또, GPU 코어도 내부 버스가 병목이라 볼 수 있는 성능의 제약이 있다고 했다.그러나, 새로운 SoC에서는, 인터커넥트가 일신 된 것으로, 그러한 문제는 해소되고 있다고 보여진다.

Intel SoC의 새로운 인터커넥트의 구성은, 동사가 스케이라불에 CPU 코어나 GPU 코어를 늘릴 수 있게 된 것도 시사하고 있다.4 CPU 코어 구성이나, GPU 코어의 대형화가 용이하게 되었다.덧붙여서, ARM SoC에서도 CPU 코어와 GPU 코어, 메모리인터페이스를 일련의 고속 인터커넥트에 접속하고 있어, 측정할 수 있는 구성이 가능하게 되어 있다.

또, GPU 코어가 Memory Fabric/North SoC Interconnect 측에 접속된 것은, 장래, CPU 코어와 GPU 코어간에 캐쉬 공유나 메모리공유의 유지를 행하는 경우에는, 중요해진다.coherency 프로토콜의 면에서도, Memory Fabric측이 충실한다고 생각할 수 있기 때문이다.

22nm 아톰세대로는, Intel은 자사내제 GPU 코어에 옮겨놓는다고 한다.그렇게 되면, GPU 코어와 CPU 코어간으로의 부분적인 캐쉬 공유, 한층 더 최종적으로는 양코어간으로의 다른 한쪽향 또는 양방향에서의 하드웨어에 의한 메모리코히렌시의 유지나 메모리 공간의 통합등의 아키텍쳐 실장이, 타사 코어를 사용하는 경우보다 훨씬 용이하게 된다.

메모리 공간의 완전한 통합에는, 메모리 어드레싱 모델의 통합이 필요하다.coherency와 통합 메모리는, GPU 코어를 범용 컴퓨팅으로 사용하는 경우에, 장기적으로 봐 매우 중요한 기능이 된다.차례로서는, 그러한 목적이 있기 위해, PowerVR로부터 자사 GPU 코어로 옮겨놓으려 하고 있을지도 모르다.무엇보다, 단순하게 메모리 대역의 확대에 의해서, PowerVR의 타일링 아키텍쳐가 불요라고 판단했을지도 모르지만.

● 다양한 IP를 지원하기위한 "IOSF"

사우스측의 IOSF/South SoC Interconnect는, SoC에서는 Rosepoint로부터 채용되었다고 ISSCC로 설명되었다.IOSF는, 많은 IP블록을 접속하기 위한 범용 버스로, 버스를 표준화 하는 것으로 IP의 재이용을 용이하게 하는 것이다.IP블록측은 같은 인터페이스 설계로, 복수 세대의 SoC에 사용해 돌릴 수 있다.SoC에서는, 옛부터 매우 일반적인 어프로치다.

ISSCC에서의 설명에 따르면 IOSF는 PCI 에뮬레이션 프로토콜로 지원한다. 따라서 IOSF는 레거시 OS에서 드라이버와의 호환성을 유지하고있다. 즉, 각 장치의 드라이버 이식이 용이하고, 소프트웨어 측면의 변경이 필요하거나 최소로 끝난다.

또한 IOSF와 다른 하위 패브릭을 지원할 수 사이드 밴드 채널을 갖추고있어 다른 상호 연결을위한 IP 블록도 지원할 수있다. Intel이 업계 관계자에 행한 설명에 따르면, 브리지 업계 표준 "OCP (Open Core Protocol)"인터커넥트도 지원한다고한다. 유연한 상호 연결, 다양한 IP를 연결 할 수있다.

쓸데없이 유연하다는 점은 Intel이지 않지만, 여기에는 사정이 있다고 추측된다. Intel은 모바일 SoC의 설계로 지금까지 자사의 IP 없었던 다양한 I / O 장치의 IP가 필요하게되었다. 그러한 IP 중에는 타사에서 구입 한 것도 포함되어 있었을 가능성도있다. 이러한 다양한 IP를 신속하게 지원하는 데 유연한 상호 연결을 필요로했을지도 모른다.

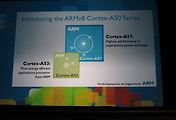

Intel SoC 상호 연결 구조는 ARM 표준 인터커넥트 인 AMBA 계통과 유사한다는 점에 유의. ARM도 계층 적 인터커넥트 구조를 채용하고있어, 최신 AMBA 4는 CPU 코어와 GPU 코어, 메모리 컨트롤러를 "CoreLink CCI-400 Cache Coherent Interconnect"에 연결하고 다른 IP를 "Network Interconnect NIC- 400 "에 연결하고있다. 상위의 상호 연결은 코어 사이의 메모리 일관성을 가지고 갈 수있다. Intel의 SoC 상호 연결 구조와 기본적으로 비슷하다.

인터커넥트 아키텍처는 SoC의 핵심이지만, 그 점에서도 Intel SoC는 ARM SoC와 같은 유연성과 융통성, 확장 성을 보장하려고하는지 알 수있다. 그렇다고해도, Intel가 흉내를 낸 같은 류의 이야기가 아니라, 이것이 합리적인 구조, Intel도 ARM도 비슷한 것으로 보인다.

따라서 Intel은 공정 기술을 SoC 용으로 개발, SoC 내부 버스를 개발하면 모바일 제품의 SoC 화를 목표로 단계를 하나 하나 올라왔다. 그리고, Intel은 앞으로도 다양한 무기를 가지고있다. 통합 전압 레귤레이터 니아 임계 숄 드 전압 회로 기술, 또한 앞으로의 이야기라면 디지털 RF 기술. 이러한 기술의 대부분은 다른 반도체 업체에 큰 차이를 내고 있기 때문에, Intel에게 큰 어드밴티지가된다.

'IT/Hardware > CPU/MB' 카테고리의 다른 글

| 인텔 하즈웰ULT에서 보여준 CPU통합칩 가능성 (0) | 2012.11.25 |

|---|---|

| 인텔 60코어「Xeon Phi」를 정식 발표 (0) | 2012.11.16 |

| TSMC 20nm 16nm 기술 로드맵을 발표 (0) | 2012.11.16 |

| ARM Cortex-A57의 정체 (0) | 2012.11.03 |

| ARM 차기 아키텍쳐 Cortex-A57과 Cortex-A53을 발표 (0) | 2012.11.03 |

| 인텔, 아톰 Z2760 스펙공개 정식출시 (2) | 2012.10.25 |

| AMD 2세대 파일드라이버아키텍쳐 비세라CPU 출시 (0) | 2012.10.23 |

| 소니 플스3 슈퍼슬림 반도체 변화 (0) | 2012.10.21 |

| 글로벌파운드리 3D FinFET 트랜지스터를 이용한 14nm XM 기술을 발표 (0) | 2012.09.25 |

| [IDF 2012] 인텔 무선충전과 4K 해상도 출력 시연 (0) | 2012.09.15 |

댓글